# TVL ST23 04 AD0

# **Specification**

Product Name Series Part No Package Size Transient Voltage Suppressor TVS Series TVL ST23 04 AD0 SOT23-6L

## **TVL ST23 04 AD0 Engineering Specification**

## 1. Scope

TVL ST23 04 AD0's are TVS arrays designed to protect high-speed signal lines from overvoltage hazard of Electrostatic Discharge (**ESD**), Electrical Fast Transients (**EFT**) and **Lightning**. These interfaces can be used in USB2.0 power and data lines, notebook and personal computers, monitors and flat panel displays, IEEE 1394 Firewire Ports, etc.

TVL ST23 04 AD0 incorporates a pair of rail-to-rail diodes with low capacitance for each of four I/O channels. Additional Zener diode is employed to minimize the influence of supply voltage. The ESD protection of TVS arrays meets the immunity standard of IEC 61000-4-2, level 4 (±15kV air, ±8kV contact discharge).

### 2. Explanation of Part Number

| <u>TV</u> | <u>L</u> | <u>ST23</u> | <u>04</u> | <u>AD0</u> |

|-----------|----------|-------------|-----------|------------|

| (1)       | (2)      | (3)         | (4)       | (5)        |

- 1. Product Type : TV=TVS Diode

- 2. Capacitance Code : L=Low Capacitance

- 3. Package Size Code

- 4. Channel Code : 04=4 Channels

- 5. Specialized Specification Code

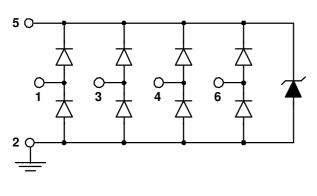

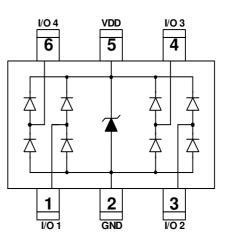

## 3. Circuit Diagram /Pin Configuration

**Circuit Diagram**

**Pin Configuration** SOT23-6L (Top-view)

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9    | Page 1 of 7          |

|----------------------------------------------------------|----------------|----------------------|

| All Specifications are subject to change without notice. | www.inpaq.com. | tw ; www.inpaggp.com |

## 4. Specifications

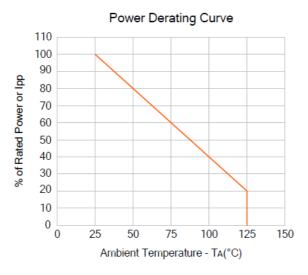

#### 4.1. ABSOLUTE MAXIMUM RATINGS

| ABSOLUTE MAXIMUM RATINGS           |                  |                            |    |

|------------------------------------|------------------|----------------------------|----|

| PARAMETER PARAMET RATING           |                  | UNITS                      |    |

|                                    | ER               |                            |    |

| Peak Pulse Current (tp =8/20 s)    | I <sub>PP</sub>  | 5.5                        | Α  |

| Operating Supply Voltage (VDD-GND) | V <sub>DC</sub>  | 6                          | V  |

| ESD per IEC 61000-4-2 (Air)        | V <sub>ESD</sub> | 15                         | kV |

| ESD per IEC 61000-4-2 (Contact)    |                  | 8                          |    |

| Lead Soldering Temperature         | T <sub>SOL</sub> | 260 (10 sec.)              | °C |

| Operating Temperature              | T <sub>OP</sub>  | -55 to +125                | °C |

| Storage Temperature                | T <sub>STO</sub> | -55 to +150                | °C |

| DC Voltage at any I/O pin          | V <sub>IO</sub>  | (GND – 0.5) to (VDD + 0.5) | V  |

#### 4.2. ELECTRICAL CHARACTERISTICS

| ELECTRICAL CHARACTERISTICS                    |                      |                                                           |   |      |      |    |

|-----------------------------------------------|----------------------|-----------------------------------------------------------|---|------|------|----|

| PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS |                      |                                                           |   |      |      |    |

| Reverse Stand-Off                             | V <sub>RWM</sub>     | Pin 5 to pin 2, T=25 °C                                   |   |      | 5    | V  |

| Voltage                                       |                      |                                                           |   |      |      |    |

| Reverse Leakage                               | I <sub>Leak</sub>    | $V_{RWM} = 5V$ , T=25 °C, Pin 5 to pin 2                  |   |      | 2    | μA |

| Current                                       |                      |                                                           |   |      |      |    |

| Channel Leakage                               | I <sub>CH Leak</sub> | V <sub>Pin 5</sub> = 5V, V <sub>Pin 2</sub> = 0V, T=25 °C |   |      | 1    | μA |

| Current                                       | _                    |                                                           |   |      |      | •  |

| Reverse Breakdown                             | V <sub>BV</sub>      | I <sub>BV</sub> = 1mA, T=25 °C                            | 6 |      |      | V  |

| Voltage                                       |                      | Pin 5 to Pin 2                                            |   |      |      |    |

| Forward Voltage                               | V <sub>F</sub>       | I <sub>F</sub> = 15mA, T=25 °C                            |   | 0.8  | 1.2  | V  |

|                                               |                      | Pin 2 to Pin 5                                            |   |      |      |    |

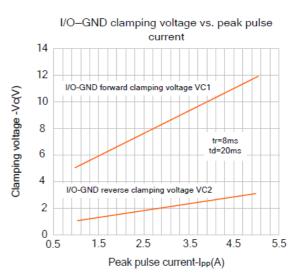

| Clamping Voltage                              | V <sub>CL</sub>      | I <sub>PP</sub> =5A, tp=8/20 s, T=25 °C                   |   | 8    | 11   | v  |

|                                               |                      | Any Channel pin to Ground                                 |   |      |      |    |

| ESD Holding Voltage                           | V <sub>hold</sub>    | IEC 61000-4-2 +6kV, T=25 °C, Contact                      |   | 14   |      | v  |

|                                               |                      | mode, Any Channel pin to Ground.                          |   |      |      |    |

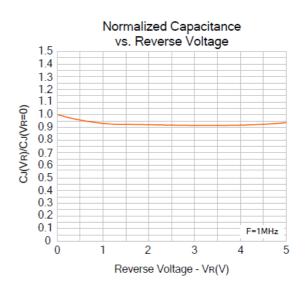

| Channel Input                                 | C <sub>IN</sub>      | $V_{pin5} = 5V, V_{pin2} = 0V, V_{IN} = 2.5V, f =$        |   | 1.0  | 1.1  | рF |

| Capacitance                                   |                      | 1MHz, T=25 °C, Any Channel pin to                         |   |      |      |    |

|                                               |                      | Ground                                                    |   |      |      |    |

| Channel to Channel                            | C <sub>CROSS</sub>   | $V_{pin5} = 5V, V_{pin2} = 0V, V_{IN} = 2.5V, f =$        |   | 0.1  | 0.12 | рF |

| Input Capacitance                             |                      | 1MHz, T=25 $^{\circ}$ C , Between Channel pins            |   |      |      |    |

| Variation of Channel                          | △C <sub>IN</sub>     | $V_{pin5} = 5V, V_{pin2} = 0V, V_{IN} = 2.5V, f =$        |   | 0.03 | 0.05 | рF |

| Input Capacitance                             |                      | 1MHz, T=25 $^{\circ}\text{C}$ , Channel_x pin to          |   |      |      |    |

|                                               |                      | Ground - Channel_y pin to Ground                          |   |      |      |    |

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9       | Page 2 of 7     |

|----------------------------------------------------------|-------------------|-----------------|

| All Specifications are subject to change without notice. | www.inpaq.com.tw; | www.inpaqgp.com |

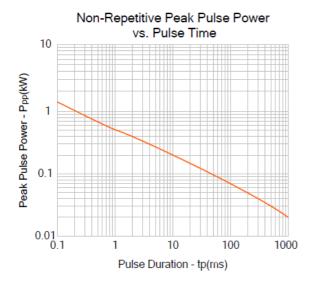

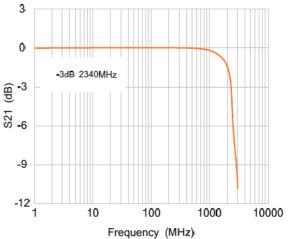

#### 4.3. TYPICAL CHARACTERISTICS

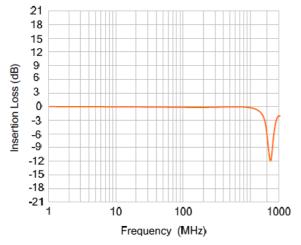

I/O - GND Insertion Loss vs. Frequency

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9      | Page 3 of 7              |

|----------------------------------------------------------|------------------|--------------------------|

| All Specifications are subject to change without notice. | www.inpaq.com.tw | ; <u>www.inpaqgp.com</u> |

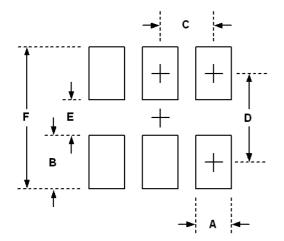

## 5. LAND LAYOUT

| Dimensions |                                               |  |  |  |

|------------|-----------------------------------------------|--|--|--|

| Millimeter | Inches                                        |  |  |  |

| 0.60       | 0.024                                         |  |  |  |

| 1.10       | 0.043                                         |  |  |  |

| 0.95       | 0.037                                         |  |  |  |

| 2.50       | 0.098                                         |  |  |  |

| 1.40       | 0.055                                         |  |  |  |

| 3.60       | 0.141                                         |  |  |  |

|            | Millimeter   0.60   1.10   0.95   2.50   1.40 |  |  |  |

Notes: This LAND LAYOUT is for reference purposes only. Please consult your manufacturing partners to ensure your company's PCB design guidelines are met.

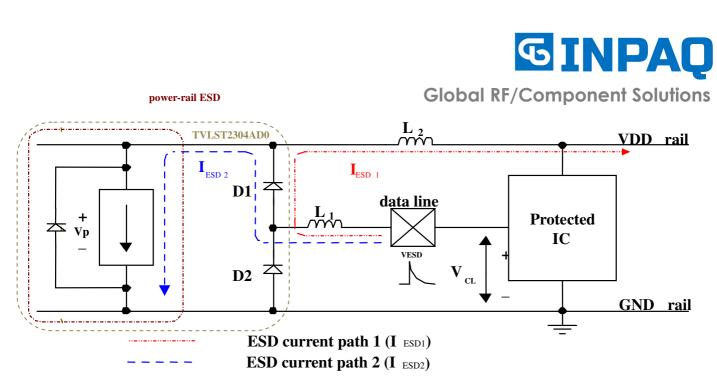

### 6. Application information

The ESD protection scheme for system I/O connector is shown in the Fig. 1. In Fig. 1, the diodes D1 and D2 are general used to protect data line from ESD stress pulse. If the power-rail ESD clamping circuit is not placed between VDD and GND rails, the positive pulse ESD current ( $I_{ESD1}$ ) will pass through the ESD current path1. Thus, the ESD clamping voltage  $V_{CL}$  of data line can be described as follow:

$V_{CL}$  = Fwd voltage drop of D1 + supply voltage of VDD rail +  $L_1 \times d(I_{ESD1})/dt + L_2 \times d(I_{ESD1})/dt$

Where  $L_1$  is the parasitic inductance of data line, and  $L_2$  is the parasitic inductance of VDD rail. An ESD current pulse can rise from zero to its peak value in a very short time. As an example, a level 4 contact discharge per the IEC61000-4-2 standard results in a current pulse that rises from zero to 30A in 1ns. Here  $d(I_{ESD1})/dt$  can be approximated by  $\Delta I_{ESD1}/\Delta t$ , or 30/(1x10-9). So just 10nH of total parasitic inductance ( $L_1$  and  $L_2$  combined) will lead to over 300V increment in  $V_{CL}$ ! Besides, the ESD pulse current which is directed into the VDD rail may potentially damage any components that are attached to that rail. Moreover, it is common for the forward voltage drop of discrete diodes to exceed the damage threshold of the protected IC. This is due to the relatively small junction area of typical discrete components. Of course, the discrete diode is also possible to be destroyed due to its power dissipation capability is exceeded.

The TVL ST23 04 AD0 has an integrated power-rail ESD clamped circuit between VDD and GND rails. It can successfully overcome previous disadvantages. During an ESD event, the positive ESD pulse current ( $I_{ESD2}$ ) will be directed through the integrated power-rail ESD clamped circuit to GND rail (ESD current path2). The clamping voltage  $V_{CL}$  on the data line is small and

protected IC will not be damaged because power-rail ESD clamped circuit offer a low impedance path to discharge ESD pulse current.

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9      | Page 4 of 7              |

|----------------------------------------------------------|------------------|--------------------------|

| All Specifications are subject to change without notice. | www.inpaq.com.tw | ; <u>www.inpaqgp.com</u> |

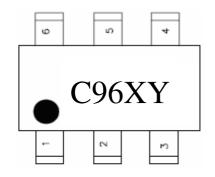

## 7. MARKING CODE Marking Code: C96X

C96 = Device Code X = Date Code Y=Control Code

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9      | Page 5 of 7              |

|----------------------------------------------------------|------------------|--------------------------|

| All Specifications are subject to change without notice. | www.inpaq.com.tw | ; <u>www.inpaqgp.com</u> |

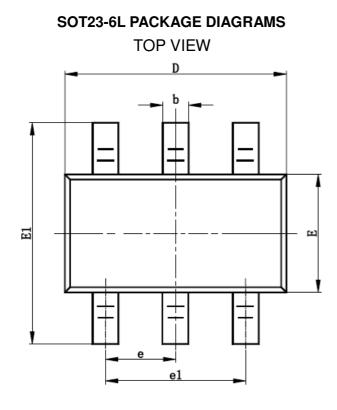

## 8. Mechanical Details

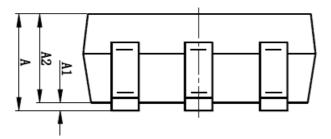

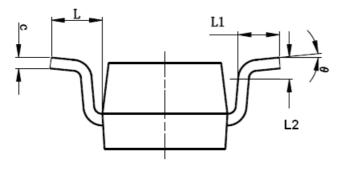

#### SIDE VIEW

END VIEW

#### PACKAGE DIMENSIONS

| Cumhal | Milimeters |      |  |

|--------|------------|------|--|

| Symbol | MIN.       | MAX. |  |

| Α      | 0.95       | 1.45 |  |

| A1     | 0.01       | 0.15 |  |

| A2     | 0.90       | 1.30 |  |

| b      | 0.30       | 0.50 |  |

| С      | 0.08       | 0.25 |  |

| D      | 2.67       | 3.17 |  |

| E      | 1.35       | 1.85 |  |

| E1     | 2.55       | 3.05 |  |

| е      | 0.95BSC    |      |  |

| e1     | 1.70       | 2.10 |  |

| L1     | 0.30       | 0.60 |  |

| L      | 0.70REF    |      |  |

| L2     | 0.25BSC    |      |  |

| θ      | 0 8        |      |  |

TVL ST23 04 AD0 Engineer Specification

■ All Specifications are subject to change without notice.

www.inpaq.com.tw ; www.inpaqgp.com

Notes:

- This dimension complies with JEDEC outline standard MO-178 Variation AB.

- Dimensioning and tolerancing per ASME Y14.5M-1994.

- All dimensions are in millimeters, and the dimensions in inches are for reference only.

- 1mm = 40 mils = 0.04 inches.

8.1. Taping Quantity:

3,000pcs/ Reel (for 7" Reel)

| TVL ST23 04 AD0 Engineer Specification                   | Version: A9      | Page 7 of 7              |

|----------------------------------------------------------|------------------|--------------------------|

| All Specifications are subject to change without notice. | www.inpaq.com.tw | ; <u>www.inpaqgp.com</u> |